PC watchでも最近よくTSVというものが出てくるようになってきました。

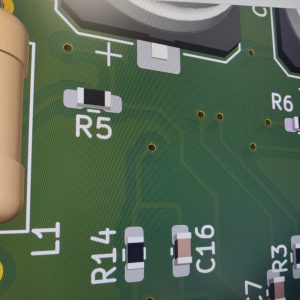

これはシリコンに貫通ビアをあけて、違うチップを重ねて実装したときに、超高密度な配線を貫通したスルーホールで行うというものです。

ワイヤーボンディングなどでもピン数が足りなくなってしまうことを解決する技術です。

なぜ、そんなに必要なのかという点についてはPC watchでも詳細に語られていますが、簡単にいうとマルチ化の波ということですね。

今までのCPUはクロックをあげることが重要でした。

それに合わせてDRAMも高速化してきましたが、クロック向上が見込めなくなりはじめて、CPUは効率の向上とマルチプロセッサに舵を切りました。

効率向上で必要なメモリーアクセスの密度が増して、さらにマルチプロセッサで倍々になり、グラフィックチップまで統合することをしても、メモリーは物理的な制約とコスト面でやたらとスロットを増やして並列アクセスをすることも出来ませんし、CPUから外部に出すピン数もハンパなく増えてしまいます。

そこで、シリコンに直接載せて超高帯域化しようということです。

TSVがねらっているのは、接続ピン数的に今のCPUのソケットピン数を越える規模の接続をすごい小さい面積で実現することです。

まあ、技術的に難しいこともありますが、究極系へシリコンウェハ上にパソコンの機能全てをいれて、電源とコネクタのみ外付けされる形になるのかもしれませんね。

TSV(シリコン貫通ビア)

投稿日:

執筆者:はざーど

まとめtyaiました【TSV(シリコン貫通ビア)】

PC watchでも最近よくTSVというものが出てくるようになってきました。これはシリコンに貫通ビアをあけて、違うチップを重ねて実装したときに、超高密度な配線を貫通したスルーホールで行うというものです。ワイヤーボンディングなどでもピン数が足りなくなってしまうこと?…